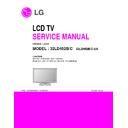

LG 32LD452B / 32LD452C (CHASSIS:LA01Z) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

B-MBA1

A-TMA13

A-TMA12

B-TMDQSLB

B-MDQSUB

A-MA6

B-MA5

0.1uF

C1224

B-TMA5

B-MDQU2

B-TMDQL6

A-MA10

A-MDQU5

B-TMDQL5

B-MDQU6

B-TMDQU5

A-MDQU2

A-TMDQU4

B-MDQL3

B-TMA1

B-MDQU3

B-TMDQU6

A-TMDQU3

10

R1207

B-MDQSLB

A-MRASB

B-MVREFCA

B-TMA9

A-TMA4

B-MDQSL

0 . 0 1 u F

25V

C1240

+1.5V_DDR

1000pF

C1202

A-TMDQL2

A-MA4

A-TMODT

B-TMDQU6

A-TMDQSLB

A-TMDQL7

A-MA2

0.1uF

C1243

A-TMDQU0

A-TMBA0

A-MDQU1

A-TMA2

B-MDQL2

240

1%

R1203

A-MDQL2

B-TMRESETB

A-TMDQL2

B-TMDQU2

0.1uF

C1241

A-TMDQL3

10K

R1232

10

R1215

0.1uF

C1211

B-TMA11

10

AR1219

B-MCASB

A-TMDQL4

B-MA13

A-MA9

0.1uF

C1228

H5TQ1G63BFR-H9C

IC1201

DDR_1333_HYNIX

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

A-MWEB

B-MCKE

A-TMA5

B-TMDMU

10

AR1217

B-MA1

A-TMA13

A-MDQU4

B-TMA12

0.1uF

C1223

0.1uF

C1245

A-TMCK

0.1uF

C1218

H5TQ1G63BFR-H9C

IC1202

DDR_1333_HYNIX

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12/BC

N7

A13

T3

A15

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_6

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

B-TMDQL7

A-MVREFCA

A-TMDML

0.1uF

C1221

0.1uF

C1203

0.1uF

C1222

A-MDMU

56

1%

R1237

1K

1%

R1225

B-MWEB

B-MCKB

0.1uF

C1220

B-TMDQL7

B-MDQL0

A-MDQU6

A-MDQU1

0.1uF

C1238

0.1uF

C1234

10

AR1214

A-TMA8

B-MDMU

10

AR1209

0.1uF

C1206

B-TMRASB

A-MDQU4

10

R1214

A-MDML

VCC_1.5V_DDR

A-MVREFCA

B-TMDQL2

B-MDQL2

B-TMA7

A-TMA7

A-TMBA0

B-MODT

B-TMA2

B-TMA12

A-TMDQL4

A-TMDQSU

A-TMA9

B-TMDMU

B-TMDQL1

A-MDQU7

B-MODT

A-TMDQL0

B-TMDQL4

A-MDQSLB

10

R1213

B-MA6

A-TMDQL0

B-TMBA2

0.1uF

C1237

B-TMA0

B-TMA3

A-MDQSL

A-MODT

VCC_1.5V_DDR

B-MA11

B-MA13

B-TMDQU7

B-MDQU7

B-TMA13

VCC_1.5V_DDR

B-TMCKB

A-TMDQU2

B-MDQU1

A-TMDQU1

B-TMDQU5

A-MDQL6

A-TMDQL5

A-TMBA1

1K

1%

R1205

0.1uF

C1215

A-TMA5

A-MDQL0

B-MVREFDQ

B-TMCKE

0.1uF

C1229

A-MCASB

10

AR1202

240

1%

1%

R1226

0.1uF

C1201

A-TMA10

B-MDQL1

B-TMDQL1

B-TMDML

1K

1%

R1201

10

AR1208

10

R1210

A-MDQL6

A-MBA2

10

R1212

B-TMDQSL

B-MDML

A-MA10

B-TMBA1

A-TMDQL1

A-TMDQU4

A-MBA0

A-MCK

10

AR1205

A-MCKE

B-MA12

B-MDQL0

B-TMDQU3

A-TMWEB

B-TMCKB

B-TMCASB

10uF

10V

10V

C1225

B-MDQSU

56

1%

R1236

B-MA8

B-TMBA2

A-MDQL2

10

AR1213

A-MDQU0

VCC_1.5V_DDR

1K

1%

R1227

B-TMDQU1

10

R1216

A-MDQU2

B-TMDQL5

B-TMDQSU

B-TMA1

B-MBA0

B-TMDQSLB

A-TMRASB

1K

1%

R1204

B-MA11

B-MA3

B-TMWEB

A-TMA1

A-MA0

A-MBA2

A-MDQU7

1K

1%

R1228

0.1uF

C1213

A-MA1

A-MCKB

A-MA2

B-MA4

A-TMA2

B-TMA10

1000pF

C1249

B-MDMU

0 . 1 u F

16V

16V

C1226

B-MDQU6

B-TMA6

B-MA7

B-MRASB

B-TMDQU0

A-TMA6

A-TMDQL5

B-TMA6

10

R1218

B-MDML

0.1uF

C1242

B-TMODT

10K

R1231

10

R1209

1000pF

C1204

B-MRASB

A-TMA9

B-TMDQL4

B-TMA0

A-TMDQU7

A-TMDQSLB

0.1uF

C1214

A-TMRASB

B-MDQU7

B-MCK

B-TMA3

B-TMDQU4

B-MBA2

B-TMA9

A-TMDQU5

A-TMA12

10

AR1201

A-TMDQU6

1000pF

C1247

A-MDQSUB

A-MCKE

10

R1223

0.1uF

C1217

A-MDQSU

B-MBA2

A-MA7

1K

1%

R1202

B-TMA8

10

R1220

B-TMDQU7

A-MRASB

A-MA1

B-TMCASB

A-TMDQU1

B-MA9

B-MDQSLB

10K

R1234

A-TMA4

B-TMDQU2

10

AR1215

B-MDQL5

B-MA0

A-TMDQSU

B-MRESETB

B-TMDML

A-MDQL3

10

AR1210

B-TMDQL3

0 . 0 1 u F

25V

C1209

A-MBA1

0.1uF

C1216

10K

R1233

B-MDQSU

0.1uF

C1250

A-TMCKB

A-TMA10

A-MA13

A-MA0

B-TMBA0

A-TMA1

B-MCK

0.1uF

C1248

B-MBA0

A-TMA0

A-MCKB

B-MA8

A-TMA11

A-MDQU0

A-MA12

56

1%

R1238

B-TMA7

10

R1208

B-MDQU3

A-MA7

B-MA0

B-MDQU4

A-TMDQSL

A-MCK

A-TMODT

A-MBA1

VCC_1.5V_DDR

B-TMA8

A-MDQU6

B-MA2

A-TMDQSUB

0.1uF

C1208

A-TMDQL3

B-MA10

B-MDQL4

LGE107D (S7M Divx_Non RM)

IC101

S7M_DIVX

A_DDR3_A0/DDR2_A13

B8

A_DDR3_A1/DDR2_A8

B9

A_DDR3_A2/DDR2_A9

A8

A_DDR3_A3/DDR2_A1

C21

A_DDR3_A4/DDR2_A2

B10

A_DDR3_A5/DDR2_A10

A22

A_DDR3_A6/DDR2_A4

A10

A_DDR3_A7/DDR2_A3

B22

A_DDR3_A8/DDR2_A6

C9

A_DDR3_A9/DDR2_A12

C23

A_DDR3_A10/DDR2_RASZ

B11

A_DDR3_A11/DDR2_A11

A9

A_DDR3_A12/DDR2_A0

C10

A_DDR3_A13/DDR2_A7

B23

A_DDR3_BA0/DDR2_BA2

B21

A_DDR3_BA1/DDR2_CASZ

A11

A_DDR3_BA2/DDR2_A5

A23

A_DDR3_MCLK/DDR2_MCLK

A12

A_DDR3_MCLKZ/DDR2_MCLKZ

C11

A_DDR3_CKE/DDR2_DQ5

B12

A_DDR3_ODT/DDR2_ODT

C20

A_DDR3_RASZ/DDR2_WEZ

A20

A_DDR3_CASZ/DDR2_BA1

B20

A_DDR3_WEZ/DDR2_BA0

A21

A_DDR3_RESETB

C22

A_DDR3_DQSL/DDR2_DQS0

C16

A_DDR3_DQSLB/DDR2_DQSB0

B16

A_DDR3_DQSU/DDR2_DQSB1

A16

A_DDR3_DQSUB/DDR2_DQS1

C15

A_DDR3_DML//DDR2_DQ13

A14

A_DDR3_DMU/DDR2_DQ6

B18

A_DDR3_DQL0/DDR2_DQ3

C18

A_DDR3_DQL1/DDR2_DQ7

B13

A_DDR3_DQL2/DDR2_DQ1

A19

A_DDR3_DQL3/DDR2_DQ10

C13

A_DDR3_DQL4/DDR2_DQ4

C19

A_DDR3_DQL5/DDR2_DQ0

A13

A_DDR3_DQL6/DDR2_CKE

B19

A_DDR3_DQL7/DDR2_DQ2

C12

A_DDR3_DQU0/DDR2_DQ15

A15

A_DDR3_DQU1/DDR2_DQ9

A17

A_DDR3_DQU2/DDR2_DQ8

B14

A_DDR3_DQU3/DDR2_DQ11

C17

A_DDR3_DQU4/DDR2_DQM1

B15

A_DDR3_DQU5/DDR2_DQ12

A18

A_DDR3_DQU6/DDR2_DQM0

C14

A_DDR3_DQU7/DDR2_DQ14

B17

B_DDR3_A0/DDR2_A13

A25

B_DDR3_A1/DDR2_A8

B24

B_DDR3_A2/DDR2_A9

A24

B_DDR3_A3/DDR2_A1

P25

B_DDR3_A4/DDR2_A2

C24

B_DDR3_A5/DDR2_A10

P26

B_DDR3_A6/DDR2_A4

B26

B_DDR3_A7/DDR2_A3

R24

B_DDR3_A8/DDR2_A6

B25

B_DDR3_A9/DDR2_A12

T26

B_DDR3_A10/DDR2_RASZ

D24

B_DDR3_A11/DDR2_A11

A26

B_DDR3_A12/DDR2_A0

C25

B_DDR3_A13/DDR2_A7

T25

B_DDR3_BA0/DDR2_BA2

P24

B_DDR3_BA1/DDR2_CASZ

C26

B_DDR3_BA2/DDR2_A5

R26

B_DDR3_MCLK/DDR2_MCLK

D26

B_DDR3_MCLKZ/DDR2_MCLKZ

D25

B_DDR3_CKE/DDR2_DQ5

E24

B_DDR3_ODT/DDR2_ODT

N25

B_DDR3_RASZ/DDR2_WEZ

M26

B_DDR3_CASZ/DDR2_BA1

N24

B_DDR3_WEZ/DDR2_BA0

N26

B_DDR3_RESETB

R25

B_DDR3_DQSL/DDR2_DQS0

J 2 5

B_DDR3_DQSLB/DDR2_DQSB0

J 2 4

B_DDR3_DQSU/DDR2_DQSB1

H26

B_DDR3_DQSUB/DDR2_DQS1

H25

B_DDR3_DML/DDR2_DQ13

F26

B_DDR3_DMU/DDR2_DQ6

L24

B_DDR3_DQL0/DDR2_DQ3

L25

B_DDR3_DQL1/DDR2_DQ7

F24

B_DDR3_DQL2/DDR2_DQ1

L26

B_DDR3_DQL3/DDR2_DQ10

F25

B_DDR3_DQL4/DDR2_DQ4

M25

B_DDR3_DQL5/DDR2_DQ0

E26

B_DDR3_DQL6/DDR2_CKE

M24

B_DDR3_DQL7/DDR2_DQ2

E25

B_DDR3_DQU0/DDR2_DQ15

G26

B_DDR3_DQU1/DDR2_DQ9

J 2 6

B_DDR3_DQU2/DDR2_DQ8

G24

B_DDR3_DQU3/DDR2_DQ11

K25

B_DDR3_DQU4/DDR2_DQM1

H24

B_DDR3_DQU5/DDR2_DQ12

K26

B_DDR3_DQU6/DDR2_DQM0

G25

B_DDR3_DQU7/DDR2_DQ14

K24

B-MA10

A-MDQU5

A-TMDQSL

B-MA2

A-MA11

0.1uF

C1219

B-MVREFCA

A-MDQL1

A-MDQL7

B-MDQL5

A-TMBA1

VCC_1.5V_DDR

A-MA5

B-MCKE

10

R1222

A-MDQU3

B-TMDQU4

0.1uF

C1233

A-TMRESETB

B-MA1

A-MCASB

B-MA12

B-TMWEB

B-TMDQU1

A-MDQL0

A-MDQU3

A-TMA0

0.1uF

C1231

A-MDQL5

A-TMRESETB

A-MBA0

B-MA4

A-TMDQU6

A-TMCASB

B-TMBA1

B-TMDQSU

B-MDQSL

B-MA7

A-TMDQU5

10

AR1206

A-MA8

A-MODT

B-TMDQL6

A-TMDQU2

A-TMDMU

B-TMA10

B-MCASB

0.1uF

C1232

A-MDML

0.1uF

C1235

A-TMCK

10

AR1220

B-MDQU0

A-TMDQL6

A-MDQSL

A-MVREFDQ

A-MDMU

A-MDQL7

0.1uF

C1244

B-TMCK

B-MDQU5

B-MDQSUB

10

R1206

10

AR1207

10

AR1218

A-MDQSUB

B-TMDQSUB

L1201

A-MRESETB

B-MDQU2

A-TMDQU7

0.1uF

C1212

B-MDQU5

B-TMDQL0

10uF

C1246

A-MDQSLB

B-MWEB

A-TMDQU3

B-MDQL7

A-TMCKB

B-TMCKE

A-TMA6

B-TMCK

10

R1211

A-TMA3

B-MDQL7

A-TMDQL6

A-TMWEB

A-MWEB

B-TMA2

B-TMA4

A-TMA11

A-MVREFDQ

A-MA3

B-MDQL1

0.1uF

C1230

B-MBA1

0.1uF

C1207

B-TMDQSUB

A-TMBA2

A-MA11

A-MA4

A-MDQSU

VCC_1.5V_DDR

B-MA5

10uF

C1205

B-TMDQSL

B-TMDQU3

A-MA3

A-MCKE

0.1uF

C1210

B-MCKE

A-TMDQL1

10

AR1216

56

1%

R1235

A-MA12

A-MA5

A-MA6

A-TMDML

B-MVREFDQ

A-MA13

A-MDQL1

10

R1221

VCC_1.5V_DDR

B-TMDQL0

A-MA8

VCC_1.5V_DDR

10

R1219

10

AR1212

B-TMRESETB

B-MDQL4

A-TMDQU0

B-TMA13

B-MRESETB

A-TMA8

B-MA9

B-TMA11

B-MA3

B-MCKB

B-TMODT

B-MDQU4

A-TMDMU

B-TMRASB

10

AR1204

B-MDQU0

B-MDQL6

B-MDQL6

10

R1217

B-MDQU1

10

AR1211

B-MDQL3

A-MDQL4

B-MA6

B-TMDQL2

B-TMDQL3

A-MDQL5

A-MRESETB

A-TMCKE

A-TMBA2

B-TMA4

0.1uF

C1239

B-TMBA0

A-MA9

B-TMA5

A-TMCASB

0.1uF

C1227

VCC_1.5V_DDR

0.1uF

C1236

A-TMA7

A-MDQL4

B-TMDQU0

A-MDQL3

VCC_1.5V_DDR

A-TMCKE

1K

1%

R1224

A-TMDQL7

A-TMA3

A-TMDQSUB

10

AR1203

NT5CB64M16AP-CG

IC1201-*1

DDR_1333_NY

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12

N7

NC_6

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_7

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

NT5CB64M16AP-CG

IC1202-*1

DDR_1333_NY

A0

N3

A1

P7

A2

P3

A3

N2

A4

P8

A5

P2

A6

R8

A7

R2

A8

T8

A9

R3

A10/AP

L7

A11

R7

A12

N7

NC_6

T3

NC_5

M7

BA0

M2

BA1

N8

BA2

M3

CK

J 7

CK

K7

CKE

K9

CS

L2

ODT

K1

RAS

J 3

CAS

K3

WE

L3

RESET

T2

DQSL

F3

DQSL

G3

DQSU

C7

DQSU

B7

DML

E7

DMU

D3

DQL0

E3

DQL1

F7

DQL2

F2

DQL3

F8

DQL4

H3

DQL5

H8

DQL6

G2

DQL7

H7

DQU0

D7

DQU1

C3

DQU2

C8

DQU3

C2

DQU4

A7

DQU5

A2

DQU6

B8

DQU7

A3

VREFCA

M8

VREFDQ

H1

ZQ

L8

VDD_1

B2

VDD_2

D9

VDD_3

G7

VDD_4

K2

VDD_5

K8

VDD_6

N1

VDD_7

N9

VDD_8

R1

VDD_9

R9

VDDQ_1

A1

VDDQ_2

A8

VDDQ_3

C1

VDDQ_4

C9

VDDQ_5

D2

VDDQ_6

E9

VDDQ_7

F1

VDDQ_8

H2

VDDQ_9

H9

NC_1

J 1

NC_2

J 9

NC_3

L1

NC_4

L9

NC_7

T7

VSS_1

A9

VSS_2

B3

VSS_3

E1

VSS_4

G8

VSS_5

J 2

VSS_6

J 8

VSS_7

M1

VSS_8

M9

VSS_9

P1

VSS_10

P9

VSS_11

T1

VSS_12

T9

VSSQ_1

B1

VSSQ_2

B9

VSSQ_3

D1

VSSQ_4

D8

VSSQ_5

E2

VSSQ_6

E8

VSSQ_7

F9

VSSQ_8

G1

VSSQ_9

G9

C L o s e t o S a t u r n 7 M I C

Close to DDR Power Pin

C L o s e t o S a t u r n 7 M I C

DDR3 1.5V By CAP - Place these Caps near Memory

Close to DDR Power Pin

CLose to DDR3

DDR3 1.5V By CAP - Place these Caps near Memory

CLose to DDR3

GP2_Saturn7M

14

DDR_256

0 . 1 u F

C2928

ISDB_DEMOD

0 . 1 u F

16V

C2912

ISDB_DEMOD

0 . 1 u F

16V

C2916

ISDB_DEMOD

FE_TS_DATA[0]

+3.3V_DE

0 . 1 u F

C2901

ISDB_DEMOD

IF_N_EXT

0 . 1 u F

C2909

ISDB_DEMOD

0 . 1 u F

C2925

ISDB_DEMOD

1M

ISDB_OPT

R2909

IF_AGC_ISDB

0 . 1 u F

16V

C2918

ISDB_DEMOD

15pF

50V

50V

C2915

ISDB_DEMOD

TP2905

ISDB_DEMOD

2.2K

R2904

ISDB_DEMOD

0 . 1 u F

16V

C2922

ISDB_DEMOD

FE_TS_DATA[0]

0 . 1 u F

C2907

ISDB_DEMOD

0 . 1 u F

C2927

ISDB_DEMOD

0 . 1 u F

16V

C2913

ISDB_DEMOD

0 . 1 u F

C2926

ISDB_DEMOD

0 . 1 u F

C2905

ISDB_DEMOD

0 . 1 u F

16V

C2914

ISDB_DEMOD

IF_P_EXT

TP2903

ISDB_DEMOD

0 . 1 u F

C2904

ISDB_DEMOD

22

R2912

ISDB_DEMOD

MN884433

ISDB_DEMOD

IC2901

1

VSS_1

2

AVDD_S

3

A I I _ S

4

AIQ_S

5

AVSS_S

6

VRT_S

7

VRB_S

8

TCPO_S

9

VDDL_1

10

MSCL_S

11

MSDA_S

12

VSS_2

13

VSSH

14

PSEL

15

ZSEL

16

VDDL_2

17

ACKI

18

TCPO_T

19

IR_T

20

VRT_T

21

VRB_T

22

AVDD_T

23

AIN_T

24

AIP_T

25

AVSS_T

26

VSS_3

27

MSCL_T

28

MSDA_T

29

VDDH_1

30

GPO1

31

AGCI_T

32

AGCR_T

33

GPO0

34

VDDL_3

35

VSS_4

36

XO

37

XI

38

VDDH_2

39

GPI1

40

GPI0

41

TEST4

42

SHVPP

43

SHVDDH

44

NC_1

45

VSS_5

46

VDDL_4

47

TCK

48

TDI

49

NRST

50

TEST3

51

VSS_6

52

VDDL_5

53

TRST

54

TMS

55

CSEL0

56

CSEL1

57

TDO

58

SYNCA

59

ERRA

60

SYNCB

61

ERRB

62

VSS_7

63

VDDL_6

64

SADR_T

65

NC_2

66

SADR_S

67

HDVDDL0

68

VSS_8

69

SDA

70

SCL

71

VDDH_3

72

SADR

73

INTA

74

INTB

75

VSS_9

76

TEST1

77

TEST2

78

SCKA

79

GPI2

80

SDOA

81

PCKA

82

DENA

83

VDDH_4

84

VSS_10

85

HDVPP

86

RON

87

NC_3

88

HDVDDH

89

NC_4

90

HDVDDL1

91

VSS_11

92

VDDL_7

93

SCKB

94

TEST0

95

SDOB

96

PCKB

97

DENB

98

GPO2

99

VDDH_5

100

AGC_S

FE_TS_DATA[0-7]

22

R2910

ISDB_DEMOD

+1.2V_DE

0 . 1 u F

C2902

ISDB_DEMOD

0 . 1 u F

C2908

ISDB_DEMOD

22

R2913

ISDB_DEMOD

FE_TS_SYNC

TP2906

ISDB_DEMOD

0 . 1 u F

C2903

ISDB_DEMOD

25MHz

X2901

ISDB_DEMOD

10K

1%

R2903

ISDB_DEMOD

0 . 1 u F

16V

C2923

ISDB_DEMOD

0 . 1 u F

C2910

ISDB_DEMOD

FE_TS_VAL_ERR

2.2K

R2914

OPT

TP2904

ISDB_DEMOD

TP2907

ISDB_DEMOD

DEMOD_SCL

0 . 1 u F

16V

C2924

ISDB_DEMOD

0 . 1 u F

16V

C2917

ISDB_DEMOD

2.2K

R2905

ISDB_DEMOD

DEMOD_RESET

10K

R2906

ISDB_DEMOD

2.2K

R2915

OPT

22

R2911

ISDB_DEMOD

TP2901

ISDB_DEMOD

0 . 1 u F

16V

C2921

ISDB_DEMOD

FE_TS_CLK

2.2K

R2908

ISDB_DEMOD

2.2K

R2907

ISDB_DEMOD

+3.3V_DE

0 . 1 u F

16V

C2920

ISDB_DEMOD

15pF

50V

50V

C2919

ISDB_DEMOD

DEMOD_SDA

0 . 1 u F

16V

C2911

ISDB_DEMOD

TP2902

ISDB_DEMOD

0 . 1 u F

C2906

ISDB_DEMOD

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+3.3V_DE

BLM18PG121SN1D

L3001

ISDB_POWER

IF_AGC

TP3002

0

ISDB_DEMOD

R3001

0.1uF

C3001

ISDB_POWER

0 . 1 u F

16V

C3005

ISDB_POWER

0 . 1 u F

16V

C3003

ISDB_POWER

10K

R3003

ISDB_POWER

IF_AGC_SEL

5.1K

R3004

ISDB_POWER

IF_AGC_MAIN

+3.3V_Normal

0

MSTAR DEMOD

R3002

SC4215ISTRT

IC3001

ISDB_POWER

3

VIN

2

EN

4

NC_2

1

NC_1

5

NC_3

6

VO

7

ADJ

8

GND

22uF

16V

16V

C3006

ISDB_POWER

IF_AGC_ISDB

+3.3V_DE

10uF

10V

10V

C3004

ISDB_POWER

+1.2V_DE

0.1uF

C3002

ISDB_POWER

FE_TS_DATA[1]

FE_TS_DATA[3]

FE_TS_DATA[0]

FE_TS_DATA[7]

FE_TS_DATA[2]

FE_TS_DATA[6]

FE_TS_DATA[5]

FE_TS_DATA[4]

MN884433

PANASONIC

AMP_I2C HAVE PULL-UP

(FE_TS_SERIAL)

(FE_TS_SERIAL)

(ISDB-T)

P o w e r ( 3 . 3 V , 1 . 2 V )

IF AGC SELECTION

GP2_Saturn7M

13

ISDB DEMOD

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

0 . 1 u F

16V

C5022

10uF

10V

10V

RF_AGC_OPT

C5027

0 . 0 1 u F

25V

25V

BOOSTER_OPT

C5011

+3.3V_TU

0 . 1 u F

16V

RF_S/W_OPT

C5002

ISA1530AC1

BOOSTER_OPT

Q5001

E

B

C

ISA1530AC1

Q5004

E

B

C

+3.3V_TU

2SC3052

BOOSTER_OPT

Q5002

E

B

C

0 . 1 u F

16V

16V

C5028

AZ1117H-ADJTRE1(EH11A)

IC5001

2

OUTPUT

3

INPUT

1

ADJ/GND

220

R5030

NON_TU_CVBS_BYPASS

1.2K

R5020

2.2K

BOOSTER_OPT

R5017

+3.3V_TU

0 . 1 u F

16V

16V

RF_AGC_OPT

C5026

+5V_TU

4.7K

R5025

10

R5036

0

R5003

220

R5031

NON_TU_CVBS_BYPASS

100

DEMOD_OPT

R5006

TU_CVBS

100pF

50V

50V

C5006

10K

BOOSTER_OPT

R5021

BLM18PG121SN1D

L5003

10uF

10V

10V

C5029

0 . 1 u F

16V

C5024

IF_AGC_SEL

0 . 1 u F

16V

C5003

0 . 1 u F

16V

C5021

18pF

50V

50V

C5012

1K

OPT

R5027

+5V_TU

TUNER_RESET

1K

OPT

R5026

+5V_TU

0 . 1 u F

16V

16V

C5016

OPT

IF_P_EXT

0

R5024

18pF

50V

50V

C5013

+5V_TU

TU_SIF

2SC3052

RF_AGC_OPT

Q5003

E

B

C

100

R5009

33

R5016

10K

RF_AGC_OPT

R5028

1.2K

R5038

0 . 1 u F

16V

C5007

0

RF_AGC_OPT

R5001

1

R5033

0

RF_S/W_OPT

R5002

+3.3V_TU

100pF

50V

50V

C5001

+5V_Normal

0 . 1 u F

16V

16V

C5023

+1.2V/+1.8V_TU

ISA1530AC1

Q5005

NON_TU_CVBS_BYPASS

E

B

C

1.2K

R5018

TU_SCL

22uF

16V

16V

OPT

C5018

33

R5015

0

NON_DEMOD_OPT

R5035

TDVJ-H001F

TU5001

NTSC_1INPUT_H_LGIT

14

3.3V

13

1.2V

5

AS

12

GND

11

VIDEO

2

BST_CNTL

10

NC

4

NC[RF_AGC]

1

ANT_PWR[OPT]

17

DIF_1

9

S I F

8

NC(IF_TP)

3

+B

16

IF_AGC_CNTL

7

SDA

6

SCL

15

RESET

18

DIF_2

SHIELD

19

IF_P_MSTAR

1K

R5022

+3.3V_Normal

22uF

16V

16V

C5019

IF_N_MSTAR

0

BOOSTER_OPT

R5014

LNA2_CTL

470

R5029

RF_SWITCH_CTL

+3.3V_TU

0 . 1 u F

16V

C5031

22uF

16V

16V

C5020

0

TU_CVBS_BYPASS

R5039

IF_N_EXT

82

R5032

TU_SDA

IF_AGC

10K

BOOSTER_OPT

R5019

0 . 1 u F

16V

C5025

100K

R5011

0 . 1 u F

16V

C5010

+1.2V/+1.8V_TU

+5V_TU

CONTROL_ATTEN

22uF

16V

16V

OPT

C5017

100

DEMOD_OPT

R5007

MLB-201209-0120P-N2

BOOSTER_OPT

L5001

BLM18PG121SN1D

L5002

0

NON_DEMOD_OPT

R5034

UDA45AL

TU5001-*1

NTSC_1INPUT_H_SANYO

14

3.3V

13

1.2V

5

AS

12

GND

11

VIDEO

2

BST_CNTL

10

NC

4

NC[RF_AGC]

1

ANT_PWR[OPT]

17

DIF_1

9

S I F

8

NC(IF_TP)

3

+B

16

IF_AGC_CNTL

7

SDA

6

SCL

15

RESET

18

DIF_2

SHIELD

19

MDS61887705

M1

SMD GASKET

OPTION : RF S/W

G P I O m u s t b e a d d e d .

T h i s w a s b e i n g a p p l i e d t o t h e o n l y c h i n a d e m o d ,

s o t h i s h a s t o b e d e l e t e d i n b o t h m a i n a n d I S D B s h e e t .

s h o u l d b e g u a r d e d b y g r o u n d

2 . A D D o f T U N E R P / N ( w . s . J e o n g _ 1 1 1 6 )

200mA

OPTION : BOOSTER

2 ) R 5 0 3 0 , R 5 0 3 1 : 2 0 0 / 1 6 0 8 T y p e = = > 2 2 0 / 2 0 1 2 T y p e ( w . s . J e o n g _ 1 1 1 6 )

C l o s e t o t h e t u n e r

V e r 1 . 0 - - > 1 . 1 : C h a n g e o f c h i p t y p e , 0 9 1 0 1 9 , w . s . j e o n g

1 ) R 5 0 2 9 , R 5 0 3 0 , R 5 0 3 1 : 1 0 0 5 T y p e = = > 1 6 0 8 T y p e ( w . s . J e o n g _ 1 0 1 9 )

60mA

1 . D e - r e t i n g

T h e p u l l - u p / d o w n o f L N A 2 _ C T L

is depended on MODLE_OPT_1.

GPIO must be added for FE_BOOSTER_CTL

LGIT CAN H/N TUNER for US

* C h a n g e H i s t o r y .

OPTION : RF AGC

P u l l - u p c a n ’ t b e a p p l i e d

because of MODEL_OPT_2

GP2_Saturn7M

12

TUNER

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

1 0 4 0 6 0 - 6 0 1 7

P702

MINI_LVDS

1

GND

2

Z_OUT

3

CLK1

4

CLK2

5

CLK3

6

CLK4

7

CLK5

8

CLK6

9

VGI_N

10

VGI_P

11

VGH_ODD

12

VGH_EVEN

13

VSS

14

VST

15

GND

16

VCOM_FB

17

VCOM_IN

18

GND

19

VDD

20

VDD

21

HALF_VDD

22

HALF_VDD

23

GND

24

VCC

25

VCC

26

GND

27

RV0+

28

RV0-

29

RV1+

30

RV1-

31

RV2+

32

RV2-

33

RVCLK+

34

RVCLK-

35

RV3+

36

RV3-

37

RV4+

38

RV4-

39

RV5+

40

RV5-

41

GND

42

SOE

43

POL

44

VST_IN

45

H_CONV

46

OPT_N

47

GND

48

GMA18

49

GMA16

50

GMA15

51

GMA13

52

GMA12

53

GMA10

54

GMA9

55

GMA7

56

GMA6

57

GMA4

58

GMA3

59

GMA1

60

GND

61

.

0

OPT

R714

VGI_N

RXB4-

Z_OUT

VCOMLFB

0

NON_GIP

R753

10uF

MINI_LVDS

C702

0 NON_GIP

R770

SOE

RXA4+

GMA16

I2C_SCL

0

NON_GIP

R749

120-ohm

WAFER_HD

L701

HVDD

CLK3

RXACK+

RXC3-

RXB2+

GSP/GVST_I

10uF

MINI_LVDS

C705

VST

0

R717

OPT

3.3K

R703

MINI_LVDS

0

NON_SCAN

R713

RXC0+

RXC2+

RXD4+

I2C_SDA

0

NON_GIP

R752

RXB3+

RXA2-

VDD_LCM

33

R707

240Hz/3D

RXA3-

VGH_M

(+25V)

1000pF

50V

50V

C709

WAFER_FHD

RXD0-

RXC0+

CLK4

SCAN_BLK1/OPC_OUT

RXC1-

RXD1-

VCOML

0

OPT

R721

RXB0-

RXC1-

120-ohm

3D

L703

1 0 4 0 6 0 - 6 0 1 7

P701

MINI_LVDS

1

GND

2

GMA1

3

GMA3

4

GMA4

5

GMA6

6

GMA7

7

GMA9

8

GMA10

9

GMA12

10

GMA13

11

GMA15

12

GMA16

13

GMA18

14

GND

15

OPT_N

16

H_CONV

17

VST_IN

18

POL

19

SOE

20

GND

21

LV0+

22

LV0-

23

LV1+

24

LV1-

25

LV2+

26

LV2-

27

LVCLK+

28

LVCLK-

29

LV3+

30

LV3-

31

LV4+

32

LV4-

33

LV5+

34

LV5-

35

GND

36

VCC

37

VCC

38

GND

39

HALF_VDD

40

HALF_VDD

41

VDD

42

VDD

43

GND

44

VCOM_IN

45

VCOM_FB

46

GND

47

VST

48

VSS

49

VGH_EVEN

50

VGH_ODD

51

VGI_P

52

VGI_N

53

CLK6

54

CLK5

55

CLK4

56

CLK3

57

CLK2

58

CLK1

59

Z_OUT

60

GND

61

.

GMA9

10uF

16V

16V

OPT

C700

OPC_EN

RXA1+

GOE/GCLK1_I

RXC0-

10K

BIT_SEL_LOW

R709

RXB0+

RXA3-

HVDD

RXC0-

TF05-41S

P704

WAFER_FHD_120HZ

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

GMA7

RXA2-

POL

RXDCK+

RXC4-

0 NON_GIP

R768

RXBCK-

RXBCK+

GMA6

CLK4

VCOMRFB

0

R716

WAFER_HD

VGL

( - 5 V )

RXA1-

0 GIP

R729

GMA13

PANEL_VCC

0 NON_GIP

R772

33

R708

240Hz/3D

3.3K

R700

MINI_LVDS

0MINI_LVDS

R754

PANEL_VCC

GMA16

PANEL_VCC

RXA3+

33

R706

240Hz

0 . 0 1 u F

50V

50V

C708

MINI_LVDS

PWM_DIM

GMA12

RXA4-

RXA2+

VCC_LCM

RXB2-

GMA4

RXC4-

RXA0-

GMA4

RXA1+

PWM_DIM

OPC_EN

RXB4+

RXA3+

VCC_LCM

GMA9

VDD_LCM

FRC_RESET

RXD1+

RXCCK+

VGL

( - 5 V )

RXD3-

GMA18

VDD_ODD

RXD1+

RXC2-

CLK2

RXB0-

RXACK+

RXC3-

VCC_LCM

10uF

16V

16V

C711

MINI_LVDS

+3.3V_Normal

0 NON_GIP

R769

CLK1

VGL_I

RXA1+

GMA7

0

R728

OPT

RXB3+

0 GIP

R701

VGI_N

10K

LVDS_SEL_LOW

R711

3.3K

LVDS_SEL_HIGH

R712

GMA3

SCAN_BLK2

33

3D

R704

Z_OUT

10uF

16V

16V

C712

MINI_LVDS

GMA15

GMA10

3.3K

NON_GIP

R773

VST

0 . 1 u F

16V

16V

C701

MINI_LVDS

0

NON_GIP

R748

GMA10

RXC3+

VGI_P

0

OPT

R724

RXD0+

0 NON_GIP

R745

RXCCK-

RXA0+

GMA3

VDD_ODD

POL

RXC4+

RXD0-

1000pF

50V

50V

3D

C714

CLK5

RXB2-

0 . 1 u F

16V

16V

C706

MINI_LVDS

120-ohm

WAFER_FHD

L702

/3D_FPGA_RESET

GMA18

VCC_LCM

RXB3-

CLK2

0 NON_GIP

R771

GMA13

VDD_EVEN

RXB1+

0 . 1 u F

16V

16V

3D

C715

0 GIP

R765

GMA6

+3.3V_Normal

RXA0+

GSC/GCLK3_I

RXB1-

CLK6

0

NON_GIP

R750

3.3K

LVDS_SEL_HIGH

R705

RXA0+

RXA0-

VDD_EVEN

RXB3-

GMA12

H_CONV

0 . 1 u F

50V

50V

C707

MINI_LVDS

RXD0+

RXC1+

10K

LVDS_SEL_LOW

R710

CLK1

RXA2+

RXD4-

VCOMR

0 . 0 1 u F

50V

50V

C703

MINI_LVDS

RXA1-

RXB4-

GMA1

FF10001-30

P705

WAFER_HD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

RXC4+

VCC_LCM

0 . 1 u F

16V

16V

C710

WAFER_FHD

CLK3

RXC2-

RXDCK-

H_CONV

0

NON_GIP

R751

0

OPT

R723

VGL_I

RXD2+

0 NON_GIP

R767

10uF

16V

16V

OPT

C713

RXACK-

0 . 1 u F

50V

50V

C704

MINI_LVDS

SOE

RXB0+

RXC1+

TF05-51S

P703

WAFER_FHD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

RXB1+

VGI_P

RXA1-

CLK5

RXD2-

GSP/GVST_I

OPC_OUT

33

3D

R702

RXA0-

GMA15

RXC3+

RXACK-

RXD1-

RXB1-

3D_POWER_EN

RXB4+

RXC2+

GMA1

CLK6

0

R720

OPT

RXB2+

RXD3+

1 0 u F / 2 5 V ( 3 2 1 6 )

LVDS_SEL

BIT_SEL

LVDS_SEL

[ 3 0 P i n L V D S C o n n e c t o r ]

(For HD 60Hz_Normal)

[LEFT FFC Connector]

( 6 0 P i n M i n i - L V D S )

[ 5 1 P i n L V D S C o n n e c t o r ]

( F o r F H D 6 0 / 1 2 0 H z )

[ R i g h t F F C C o n n e c t o r ]

( 6 0 P i n M i n i - L V D S )

[ 4 1 P i n L V D S C o n n e c t o r ]

( F o r F H D 1 2 0 H z )

1 0 u F / 2 5 V ( 3 2 1 6 )

11

GP2_Saturn7M

LVDS

Click on the first or last page to see other 32LD452B / 32LD452C (CHASSIS:LA01Z) service manuals if exist.