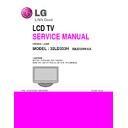

LG 32LD333H (CHASSIS:LA06H) Service Manual ▷ View online

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

0.1uF

C4058

FRC_LPLL

0 . 0 4 7 u F

C227

FRCVDDC

VDD33

BLM18PG121SN1D

L212

+1.5V_DDR

DDC_SDA_1

SIDEAV_L_IN

0.1uF

C4019

0.1uF

C4056

0.1uF

C4027

VDD33

0.1uF

C4032

10uF

C263

DDC_SCL_2

D2-_HDMI1

33

R257

100

R203

OPT

DSUB_B-

0.1uF

C4011

2 . 2 u F

C236

AVDD_DDR0

COMP1_Pr-

VDD33_DVI

BLM18PG121SN1D

L227

33

R230

TU_SDA

D1-_HDMI1

33

R4016

FE_DEMOD_SDA

COMP1_Pb-

33

R282

OPT

33

R255

+3.3V_Normal

COMP1_L_IN

IF_P_MSTAR

100

R289

0.1uF

C4038

TU_CVBS

AVDD_DDR0

+3.3V_Normal

68

R252

1000pF

OPT

C264

MODEL_OPT_0

68

R231

+1.26V_VDDC

MVREF

BLM18PG121SN1D

L219

AMP_SDA

33

R285

OPT

MODEL_OPT_1

1/16W

1K

1%

R4014

AUD_SCK

BLM18SG700TN1D

L226

HPD1

24MHz

X201

0.1uF

C283

0.1uF

C4009

0.1uF

C4002

33

R232

0 . 0 4 7 u F

C204

PC_R_IN

0 . 0 4 7 u F

C225

COMP1_Pb+

0 . 0 4 7 u F

C215

0 . 0 4 7 u F

C233

AU25

VDD_RSDS

33

R228

AVDD2P5

AVDD25_PGA

AVDD_DDR0

68

R256

33

R253

DDC_SCL_1

DSUB_B+

33

R244

22

R4024

ADC2P5

BLM18SG700TN1D

L225

AVDD_DMPLL

D0-_HDMI2

MODEL_OPT_5

2 . 2 u F

C4059

SIDE_USB_DM

22

R4018

OPT

FE_DEMOD_SCL

10K

R4023

2 . 2 u F

C244

BLM18PG121SN1D

L213

OPT

0.1uF

C4012

0 . 0 4 7 u F

C205

AVDD_DDR0

2 . 2 u F

C238

SOC_RESET

+3.3V_Normal

AVDD_DMPLL

0.1uF

C295

0.1uF

C4017

MVREF

0.1uF

C4062

0 . 0 4 7 u F

C211

0.1uF

C285

0

R236

D1+_HDMI1

0.1uF

C4023

AV_L_IN

+3.3V_Normal

1000pF

OPT

C203

BLM18PG121SN1D

L207

1/10W

0

5%

R4027

100

R201

OPT

DSUB_VSYNC

AVDD_DMPLL

0 . 0 4 7 u F

C207

AVDD25_PGA

33

R278

DSUB_HSYNC

AVDD_DDR1

D0-_HDMI1

FRC_VDD33_DDR

2 . 2 u F

C245

DSUB_G-

0.1uF

C286

2 . 2 u F

C237

1000pF

C210

0 . 1 u F

C4015

0 . 1 u F

C258

VDD33

AVDD2P5

BLM18PG121SN1D

L209

10K

R4020

0.1uF

C292

0.1uF

C294

AVDD2P5

1uF

C253

CK+_HDMI1

COMP1_Y-

100

R288

1K

R4019

VDD33

0.1uF

C4007

PC_L_IN

0 . 0 4 7 u F

C208

TP204

100

R204

OPT

AU33

+2.5V_Normal

CK-_HDMI1

+2.5V_Normal

+2.5V_Normal

D2+_HDMI1

D0+_HDMI2

0 . 0 4 7 u F

C213

0.1uF

C4003

68

R254

+2.5V_Normal

MODEL_OPT_3

0 . 0 4 7 u F

C212

SIDEAV_CVBS_IN

2 . 2 u F

C247

OPT

AMP_SCL

0.1uF

C4006

1000pF

C217

AU33

BLM18PG121SN1D

L222

47

R4002

0.1uF

C280

CK-_HDMI2

10K

R4006

0.1uF

C4013

10K

R4026

BLM18PG121SN1D

OPT

L214

+1.26V_VDDC

100

R202

OPT

BLM18PG121SN1D

L217

FRC_AVDD

D2-_HDMI2

68

R258

33

R283

OPT

0 . 0 4 7 u F

C206

0 . 0 4 7 u F

C232

0.1uF

C290

0.1uF

C4026

TU_SIF

0 . 0 4 7 u F

C231

CK+_HDMI2

0 . 0 4 7 u F

C4057

TU_SCL

TP206

0.1uF

C4036

68

R233

AUD_LRCH

BLM18PG121SN1D

L221

OPT

VDD33

MIU1VDDC

D2+_HDMI2

+1.26V_VDDC

ADC2P5

AUD_LRCK

0.1uF

C4008

1/16W

1K

1%

R4015

AV_R_IN

D1+_HDMI2

0 . 0 4 7 u F

C216

0.1uF

C4041

0.1uF

C297

DSUB_R-

1M

R287

COMP1_Y+

DSUB_G+

100

R296

D0+_HDMI1

0 . 1 u F

C256

0 . 0 4 7 u F

C214

33

R284

OPT

0.1uF

C4024

2 . 2 u F

OPT

C235

1/10W

0

5%

R4022

BLM18PG121SN1D

L215

HPD2

0.1uF

C4028

2 . 2 u F

OPT

C234

IR

0 . 0 2 2 u F

16V

16V

C4065

0 . 1 u F

C257

AUD_MASTER_CLK

0.1uF

C296

2 . 2 u F

C239

FRC_AVDD

33

R246

TP205

VDD33_DVI

47

R4003

100

R298

OPT

FRC_VDD33_DDR

0 . 1 u F

C4064

IF_N_MSTAR

0.1uF

C4014

DSUB_R+

AVDD_DDR1

33

R251

0

R234

+2.5V_Normal

0 . 0 4 7 u F

C209

0 . 1 u F

C251

AVDD2P5

SIDEAV_R_IN

0.1uF

C4016

33

R280

2 . 2 u F

C246

OPT

SIDE_USB_DP

MODEL_OPT_2

2 . 2 u F

C4060

COMP1_Pr+

TP201

33

R250

22

R4025

BLM18PG121SN1D

L211

FRC_LPLL

AV_CVBS_IN

DDC_SDA_2

0 . 1 u F

C250

68

R229

+1.26V_VDDC

TP202

AU25

VDD_RSDS

10K

R4017

OPT

0.1uF

C277

BLM18PG121SN1D

L206

0.1uF

C299

BLM18PG121SN1D

L204

FRCVDDC

0.1uF

C4040

TP203

D1-_HDMI2

0 . 1 u F

C288

VDD33

COMP1_R_IN

BLM18SG121TN1D

L202

BLM18SG121TN1D

L223

0 . 1 u F

C4005

TP208

TP210

10uF

C275

10uF

C276

10uF

C278

10uF

C281

10uF

C284

10uF

C287

10uF

C289

10uF

C293

10uF

C4001

10uF

C4018

10uF

C4022

10uF

C4061

10uF

C4063

4 . 7 u F

C249

1uF

C4045

0.1uF

C4020

0.1uF

C4025

0.1uF

C4031

MIU1VDDC

VDD33

0 OPT

R4029

0 OPT

R4028

AMP_SCL

AMP_SDA

0

R4032

0

R4033

22

R292

DEMOD_OPT

22

R291

DEMOD_OPT

1K

R227

1K

R212

1K

OPT

R226

1K

DDR_256MB

R209

1K

OPT

R211

1K

R207

HD

1K

FHD

R206

1K

DDR_512MB

R208

MODEL_OPT_4

10uF

C4066

BLM18SG700TN1D

L228

MODEL_OPT_5

MODEL_OPT_4

1K

OPT

R294

1K

R297

1K

OPT

R295

1K

OPT

R293

MIU0VDDC

MIU0VDDC

+1.26V_VDDC

10uF

C228

0.1uF

C241

0.1uF

C4042

0.1uF

C4046

0.1uF

C4043

0.1uF

C4044

27pF

C261

27pF

C262

+3.3V_Normal

10K

R205

OPT

100

OPT

R210

100

OPT

R213

MODEL_OPT_6

1K

R215

1K

OPT

R214

LGE107D (S7M Divx_Non RM)

IC101

S7M_DIVX

A_RXCP

F1

A_RXCN

F2

A_RX0P

G2

A_RX0N

G3

A_RX1P

H3

A_RX1N

G1

A_RX2P

H1

A_RX2N

H2

DDCDA_DA/GPIO24

F5

DDCDA_CK/GPIO23

F4

HOTPLUGA/GPIO19

E6

B_RXCP

D3

B_RXCN

C1

B_RX0P

D1

B_RX0N

D2

B_RX1P

E2

B_RX1N

E3

B_RX2P

F3

B_RX2N

E1

DDCDB_DA/GPIO26

D4

DDCDB_CK/GPIO25

E4

HOTPLUGB/GPIO20

D5

C_RXCP

AA2

C_RXCN

AA1

C_RX0P

AB1

C_RX0N

AA3

C_RX1P

AB3

C_RX1N

AB2

C_RX2P

AC2

C_RX2N

AC1

DDCDC_DA/GPIO28

AB4

DDCDC_CK/GPIO27

AA4

HOTPLUGC/GPIO21

AC3

D_RXCP

A2

D_RXCN

A3

D_RX0P

B3

D_RX0N

A1

D_RX1P

B1

D_RX1N

B2

D_RX2P

C2

D_RX2N

C3

DDCDD_DA/GPIO30

B4

DDCDD_CK/GPIO29

C4

HOTPLUGD/GPIO22

E5

CEC/GPIO5

D6

HSYNC0

G5

VSYNC0

G6

RIN0P

K1

RIN0M

L3

GIN0P

K3

GIN0M

K2

BIN0P

J 3

BIN0M

J 2

SOGIN0

J 1

HSYNC1

G4

VSYNC1

H6

RIN1P

K5

RIN1M

K4

GIN1P

J 4

GIN1M

K6

BIN1P

H4

BIN1M

J 6

SOGIN1

J 5

HSYNC2

H5

RIN2P

N3

RIN2M

N2

GIN2P

M2

GIN2M

M1

BIN2P

L2

BIN2M

L1

SOGIN2

M3

CVBS0P

N4

CVBS1P

N6

CVBS2P

L4

CVBS3P

L5

CVBS4P

L6

CVBS5P

M4

CVBS6P

M5

CVBS7P

K7

CVBS_OUT1

M6

CVBS_OUT2

M7

VCOM0

N5

VIFP

W2

VIFM

W1

I P

V2

IM

V1

S S I F / S I F P

Y2

SSIF/SIFM

Y1

QP

U3

QM

V3

IFAGC

Y5

RF_TAGC

Y4

TGPIO0/UPGAIN

U1

TGPIO1/DNGAIN

U2

TGPIO2/I2C_CLK

R3

TGPIO3/I2C_SDA

T3

XTALIN

T2

XTALOUT

T1

SPDIF_IN/GPIO177

G14

SPDIF_OUT/GPIO178

G13

DM_P0

B7

DP_P0

A7

DM_P1

AF17

DP_P1

AE17

I2S_IN_BCK/GPIO175

F14

I2S_IN_SD/GPIO176

F13

I2S_IN_WS/GPIO174

F15

I2S_OUT_BCK/GPIO181

D20

I2S_OUT_MCK/GPIO179

E20

I2S_OUT_SD/GPIO182

D19

I2S_OUT_SD1/GPIO183

F18

I2S_OUT_SD2/GPIO184

E18

I2S_OUT_SD3/GPIO185

D18

I2S_OUT_WS/GPIO180

E19

LINE_IN_0L

N1

LINE_IN_0R

P3

LINE_IN_1L

P1

LINE_IN_1R

P2

LINE_IN_2L

P4

LINE_IN_2R

P5

LINE_IN_3L

R6

LINE_IN_3R

T6

LINE_IN_4L

U5

LINE_IN_4R

V5

LINE_IN_5L

U6

LINE_IN_5R

V6

LINE_OUT_0L

U4

LINE_OUT_2L

W3

LINE_OUT_3L

W4

LINE_OUT_0R

V4

LINE_OUT_2R

Y3

LINE_OUT_3R

W5

MIC_DET_IN

R4

MICCM

T5

MICIN

R5

AUCOM

T4

VRM

P7

VAG

R7

VRP

P6

HP_OUT_1L

R1

HP_OUT_1R

R2

ET_RXD0

E21

ET_TXD0

E22

ET_RXD1

D21

ET_TXD1

F21

ET_REFCLK

E23

ET_TX_EN

D22

ET_MDC

F22

ET_MDIO

D23

ET_CRS

F23

AVLINK

F8

IRINT

G8

TESTPIN

K8

RESET

A4

U3_RESET

Y17

LGE107D (S7M Divx_Non RM)

IC101

S7M_DIVX

VDDC_1

H11

VDDC_2

H12

VDDC_3

H13

VDDC_4

H14

VDDC_5

H15

VDDC_6

J 1 2

VDDC_7

J 1 3

VDDC_8

J 1 4

VDDC_9

J 1 5

VDDC_10

J 1 6

VDDC_11

L18

A_DVDD

H16

B_DVDD

K19

FRC_VDDC_0

L19

FRC_VDDC_1

M18

FRC_VDDC_2

M19

FRC_VDDC_3

N18

FRC_VDDC_4

N19

FRC_VDDC_5

N20

FRC_VDDC_6

P18

FRC_VDDC_7

P19

FRC_VDDC_8

P20

U3_DVDD_DDR

Y12

AVDD1P2

J 1 1

DVDD_NODIE

L7

AVDD2P5_ADC_1

H7

AVDD2P5_ADC_2

J 7

AVDD25_REF

J 8

AVDD_AU25

L8

PVDD_1

W15

PVDD_2

Y15

AVDD25_PGA

U8

AVDD_NODIE

M8

AVDD_DVI_1

N9

AVDD_DVI_2

P9

AVDD3P3_CVBS

N8

AVDD_DMPLL

P8

AVDD_AU33

T7

AVDD_EAR33

U7

AVDD33_T

T9

VDDP_1

R8

VDDP_2

R9

VDDP_3

T8

FRC_VD33_2_1

V20

FRC_VD33_2_2

W20

FRC_AVDD_RSDS_1

U19

FRC_AVDD_RSDS_2

U20

FRC_AVDD_RSDS_3

V19

FRC_AVDD

W19

FRC_AVDD_LPLL

U18

FRC_AVDD_MPLL

T20

FRC_VDD33_DDR

Y14

AVDD_MEMPLL

R19

FRC_AVDD_MEMPLL

W14

AVDD_DDR0_D_1

D15

AVDD_DDR0_D_2

D16

AVDD_DDR0_D_3

E15

AVDD_DDR0_D_4

E16

AVDD_DDR0_C

E17

AVDD_DDR1_D_1

F16

AVDD_DDR1_D_2

F17

AVDD_DDR1_D_3

G16

AVDD_DDR1_D_4

G17

AVDD_DDR1_C

H17

FRC_AVDD_DDR_D_1

AB11

FRC_AVDD_DDR_D_2

AB12

FRC_AVDD_DDR_D_3

AC11

FRC_AVDD_DDR_D_4

AC12

FRC_AVDD_DDR_C

AA12

MVREF

G15

NC_1

Y7

NC_2

Y8

GND_1

G18

GND_2

H9

GND_3

H10

GND_4

H18

GND_5

H19

GND_6

J 1 0

GND_7

J 1 7

GND_8

J 1 8

GND_9

J 1 9

GND_10

K9

GND_11

K10

GND_12

K11

GND_13

K12

GND_14

K13

GND_15

K14

GND_16

K15

GND_17

K16

GND_18

K17

GND_19

K18

GND_20

L9

GND_21

L10

GND_22

L11

GND_23

L12

GND_24

L13

GND_25

L14

GND_26

L15

GND_27

L16

GND_28

L17

GND_29

M9

GND_30

M10

GND_31

M11

GND_32

M12

GND_33

M13

GND_34

M14

GND_35

M15

GND_36

M16

GND_37

M17

GND_38

N10

GND_39

N11

GND_40

N12

GND_41

N13

GND_42

N14

GND_43

N15

GND_44

N16

GND_45

N17

GND_46

P10

GND_47

P11

GND_48

P12

GND_49

P13

GND_50

P14

GND_51

P15

GND_52

P16

GND_53

P17

GND_54

R10

GND_55

R11

GND_56

R12

GND_57

R13

GND_58

R14

GND_59

R15

GND_60

R16

GND_61

R17

GND_62

R18

GND_63

T10

GND_64

T11

GND_65

T12

GND_66

T13

GND_67

T14

GND_68

T15

GND_69

T16

GND_70

T17

GND_71

T18

GND_72

T19

GND_73

U10

GND_74

U11

GND_75

U12

GND_76

U13

GND_77

U14

GND_78

U15

GND_79

U16

GND_80

U17

GND_81

V7

GND_82

V8

GND_83

V9

GND_84

V10

GND_85

V11

GND_86

V12

GND_87

V13

GND_88

V14

GND_89

V15

GND_90

V16

GND_91

V17

GND_92

V18

GND_93

W7

GND_94

W8

GND_95

W9

GND_96

W10

GND_97

W11

GND_98

W12

GND_99

W13

GND_100

W16

GND_101

W17

GND_102

W18

GND_103

Y13

GND_104

Y18

GND_105

AA13

GND_106

AB13

GND_107

AC13

GND_FU

J 9

PGA_VCOM

U9

GND_108

D17

GND_109

H23

GND_110

AF13

100

R216

100

R217

22K

R218

0.01uF

C218

EXT_SPK

IF_AGC_MAIN

EDID_WP

0

R260

0

R259

OPT

+3.3V_Normal

1K

R261

ANALOG SIF

RMII For Ethernet

RSDS Power OPT

FRC

I2S_I/F

PIN NAME

DSUB

N o r m a l 2 . 5 V

Close to MSTAR

MODEL OPTION

FRC_LPLL:13mA

N o r m a l P o w e r 3 . 3 V

DTV_IF

AVDD_DMPLL/AVDD_NODIE:7.362mA

FRC_MPLL:4mA

AU25:10mA

Close to MSTAR

AVDD_MEMPLL:24mA

F7

VDD33_DVI:163mA

FHD

SCART1_RGB/COMP1

G19

AVDD2P5/ADC2P5:162mA

MODEL_OPT_3

AVDD25_PGA:13mA

C5

VDDC : 2026mA

AVDD_DDR0:55mA

VDDC 1.26V

PIN NO.

NO FRC

MODEL_OPT_0

CVBS In/OUT

AUDIO OUT

TU/DEMOD_I2C

FRC_AVDD:60mA

HD

AUDIO IN

VDD_RSDS:88mA

MODEL_OPT_1

FRC_VDD33_DDR:50mA

DDR_512MB

Close to MSTAR

SIDE USB

DDR3 1.5V

VDD33_T/VDDP/U3_VD33_2:47mA

B6

MODEL OPTION

HDMI

LOW

AU33:31mA

DDR_256MB

HIGH

MODEL_OPT_2

B/T USB

Close to MSTAR

RSDS Power OPT

AVDD_DDR1:55mA

2

MINI LVDS

LVDS

MODEL_OPT_4

MODEL_OPT_5

100/120Hz LVDS

E18

GIP

NON_GIP

D18

50/60Hz LVDS

MODEL_OPT_6

F9

LCD

OLED

N O _ F R C : L O W L O W

U 3 _ I N T E R N A L : H I G H L O W

U 3 _ E X T E R N A L : H I G H H I G H

PWIZ TCON with LG FRC : HIGH HIGH

OPT_0 OPT_4

HP OUT

37LD320H

Main

2 0 1 0 . 1 2 . 2 2

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

MLB-201209-0120P-N2

L1227

3 . 3 V _ P r o i d i o m

3 . 3 V _ P r o i d i o m

+VCCINT_1.5V

0 1 2 : S 2 6 ; 0 1 2 : A J 2 6

FE_DEMOD_SCL

0 0 1 : A G 5 ; 0 0 2 : S 2 0

3 . 3 V _ P r o i d i o m

BSS83

Q1115

S

B

D

G

10uF

16V

16V

C2176

VSB_RESET

012:B17

3 . 3 V _ P r o i d i o m

0 . 1 u F

16V

16V

C2181

OPT

3 . 3 V _ P r o i d i o m

+3.3V_Normal

1uF

25V

C2179

OPT

FPGA_RESET

012:Q17

3 . 3 V _ P r o i d i o m

1uF

25V

C2255

MAX809RTR

IC1210

1

GND

3

VCC

2

RESET

MSDA_3.3V

0 . 1 u F

16V

16V

C2178

SYS_RESET

0 0 1 : A J 2 1

MLB-201209-0120P-N2

L1228

3 . 3 V _ P r o i d i o m

MSCL_3.3V

1N4148W

D1250

OPT

OPT

FE_DEMOD_SDA

0 0 1 : A G 5 ; 0 0 2 : S 2 0

+5V_Normal

DE_H_SYSCLK

012:Q17

BSS83

Q1114

S

B

D

G

27MHz

X1006

6

1

2

5

3

4

100uF

16V

16V

C2177

0 . 1 u F

16V

16V

C2180

OPT

VSB_RESET

0

R2446

0

R2447

0

R2448

0

R2449

10K

R2391

10K

R2392

1K

R2397

47K

R2396

47K

R2395

22

R2387

100

R2394

OPT

100

R2564

100

OPT

R2393

4.7K

R2563

10K

R2390

OPT

XMARK_1.8V

0 . 1 u F

16V

16V

XMARK

C2260

22uF

16V

16V

XMARK

C2261

GND

MLB-201209-0120P-N2

XMARK

L1251

AZ1117H-1.8TRE1(EH13A)

IC1240

XMARK

2

OUTPUT

3

INPUT

1

ADJ/GND

0 . 1 u F

16V

16V

XMARK

C2262

22uF

16V

16V

XMARK

C2263

3 . 3 V _ P r o i d i o m

4 . 7 u F

XMARK

C2271

3 . 3 V _ P r o i d i o m

TS_4

005:AF16

0.1uF

16V

C2208

TS_5

005:AF16

10K

R2414

0.01uF

C2191

3 . 3 V _ P r o i d i o m

0.1uF

16V

C2211

0

XMARK

R2586

MLB-201209-0120P-N2

L1235

0

LGDT1129

R2587

GND

0.1uF

16V

C2197

TS_3

005:AF17

0.01uF

25V

XMARK

C2265

10K

XMARK

R2570

MLB-201209-0120P-N2

L1234

22

R2415

0

XMARK

R2571

MLB-201209-0120P-N2

L1236

XMARK_1.8V

PM_TS_SYNC

008:AP25

0

XMARK

R2573

0.1uF

16V

C2195

0.1uF

16V

C2213

0.1uF

16V

C2201

0

XMARK

R2575

GND

10K

OPT

R2406

0.1uF

16V

C2200

XMARK_1.8V

0

XMARK

R2585

0.1uF

16V

C2209

LGDT1129

IC1209

LGDT1129

H1

CLK1

B8

IO2_29/TP_SOP

B9

IO2_21/TP_VALID

B10

IO2_17/TP_ERR

C5

IO2_41/TP_DATA[7]

C6

IO2_36/TP_DATA[6]

C7

IO2_31/TP_DATA[5]

C8

IO2_25/TP_DATA[4]

C9

IO2_23/TP_DATA[3]

C10

IO2_18/TP_DATA[2]

C11

IO2_14/TP_DATA[1]

C12

IO2_8/TP_DATA[0]

M1

IO1_29

C3

IO1_2

C2

IO1_3

B1

IO1_4

G5

IO1_5

F4

IO1_6

D3

IO1_7

E4

IO1_8

F5

IO1_9

E3

IO1_10

D2

IO1_11

E2

IO1_12

G1

CLK0

B2

IO2_48/RESET

D14

IO3_37/I2C_SCK

E14

IO3_34/I2C_SDA

K4

DCLK

K13

CONF_DONE

H3

NCONFIG

J 4

NCE

H2

DATA0

G4

IO1_21SO

K3

IO1_22/ASDO

H4

NCEO

J 1 3

NSTATUS

J 3

MSEL0

J 2

MSEL1

J 1 4

TCK

H15

TDO

J 1 5

TMS

H14

TDI

D4

IO1_1/INIT_DONE

D1

IO1_13

F3

IO1_14

G3

IO1_15

F2

IO1_16

E1

IO1_17

G2

IO1_18

F1

IO1_19

H5

IO1_20

J 1

IO1_23

K2

IO1_24

L3

IO1_25

K1

IO1_26

L1

IO1_27

L2

IO1_28

N1

IO1_30

M2

IO1_31

N2

IO1_32

M3

IO1_33

L5

IO1_34

M4

IO1_35

N3

IO1_36

K5

IO1_37

L4

IO1_38

R1

IO1_39

P2

IO1_40

P3

IO1_41

N4

IO1_42

R2

IO4_1

T2

IO4_2

R3

IO4_3

P4

IO4_4

R4

IO4_5

T4

IO4_6

R5

IO4_7

M5

IO4_9

M6

IO4_10

N5

IO4_11

N6

IO4_12

R6

IO4_14

M7

IO4_15

T6

IO4_16

R7

IO4_17

N7

IO4_19

T8

IO4_21

M8

IO4_22

N8

IO4_23

M10

IO4_25

T9

IO4_27

N9

IO4_29

T11

IO4_31

N10

IO4_32

N11

IO4_36

N12

IO4_37

M9

IO4_38

M11

IO4_39

M12

IO4_40

R12

IO4_42

T13

IO4_43

R13

IO4_44

R14

IO4_45

P13

IO4_46

T15

IO4_47

R15

IO4_48

N13

IO3_1

P14

IO3_2

P15

IO3_3

R16

IO3_4

N15

IO3_5

N16

IO3_6

K12

IO3_7

K14

IO3_8

L12

IO3_9

N14

IO3_10

M13

IO3_11

M14

IO3_12

L13

IO3_13

M15

IO3_14

M16

IO3_15

L14

IO3_16

L15

IO3_17

L16

IO3_18

K16

IO3_19

K15

IO3_20

J16

IO3_21

H16

CLK3

G16

CLK2

H12

IO3_22

G14

IO3_23

G13

IO3_24

G15

IO3_25

F16

IO3_26

F14

IO3_27

F13

IO3_28

F15

IO3_29

E16

IO3_30

E15

IO3_31

D16

IO3_32

D15

IO3_33

F12

IO3_35

E13

IO3_36

H13

IO3_38

G12

IO3_39

B16

IO3_40

C15

IO3_41

C14

IO3_42

D13

IO3_43

B15

IO2_1

A15

IO2_2

B14

IO2_3

C13

IO2_4

B13

IO2_5

A13

IO2_6

B12

IO2_7

A2

IO2_47

E12

IO2_9

E11

IO2_10

E9

IO2_11

D12

IO2_12

D11

IO2_13

B3

IO2_46

B11

IO2_15

A11

IO2_16

D10

IO2_19

A9

IO2_20

D9

IO2_22

C4

IO2_45

E10

IO2_24

B4

IO2_44

D8

IO2_26

E8

IO2_27

A8

IO2_28

D7

IO2_30

A4

IO2_43

B7

IO2_32

A6

IO2_33

E7

IO2_34

P12

IO4_41/CH_DATA[7]

P11

IO4_35/CH_DATA[6]

P10

IO4_33/CH_DATA[5]

P9

IO4_28/CH-DATA[4]

P8

IO4_24/CH_DATA[3]

P7

IO4_18/CH_DATA[2]

P6

IO4_13/CH_DATA[1]

P5

IO4_8/CH_DATA[0]

R10

IO4_30/CH_ERR

R9

IO4_26/CH_SOP

R8

IO4_20/CH_VALID

R11

IO4_34/CH_CLK

A7

VCCINT_1

A10

VCCINT_2

G8

VCCINT_3

G10

VCCINT_4

H7

VCCINT_5

H9

VCCINT_6

J8

VCCINT_7

J10

VCCINT_8

K7

VCCINT_9

K9

VCCINT_10

T7

VCCINT_11

T10

VCCINT_12

C1

VCCIO1_1

G6

VCCIO1_2

P1

VCCIO1_3

T3

VCCIO4_1

L7

VCCIO4_2

L10

VCCIO4_3

T14

VCCIO4_4

P16

VCCIO3_1

K11

VCCIO3_2

C16

VCCIO3_3

A14

VCCIO2_1

F10

VCCIO2_2

F7

VCCIO2_3

A3

VCCIO2_4

A1

GND_1

A16

GND_2

A5

GND_3

A12

GND_4

F6

GND_5

F8

GND_6

F9

GND_7

F11

GND_8

G7

GND_9

G9

GND_10

G11

GND_11

H8

GND_12

H10

GND_13

J7

GND_14

J9

GND_15

K6

GND_16

K8

GND_17

K10

GND_18

L6

GND_19

L8

GND_20

L9

GND_21

L11

GND_22

T1

GND_23

T5

GND_24

T12

GND_25

T16

GND_26

J6

GNDA_PLL1

J5

GNDG_PLL1

J11

GNDA_PLL2

J12

GNDG_PLL2

H6

VCCA_PLL1

H11

VCCA_PLL2

B6

IO2_35

B5

IO2_42

D6

IO2_37

D5

IO2_38

E6

IO2_39

E5

IO2_40

22

R2417

FPGA_RESET

010:B23

4.7K

OPT

R2418

0.1uF

16V

C2215

0.1uF

16V

C2199

0

XMARK

R2589

1uF

50V

C2185

XMARK_1.8V

TS_VALID

005:AN19

100

R2443

+VCCINT_1.5V

1uF

50V

C2192

10K

R2413

MLB-201209-0120P-N2

L1232

TS_7

005:AF16

0.1uF

16V

XMARK

C2264

0.1uF

16V

C2216

0.1uF

16V

C2214

0

XMARK

R2581

0

XMARK

R2572

BLM18PG121SN1D

XMARK

L1253

0.01uF

C2188

TS_0

005:AF17

TS_CLK

005:AN19

0.1uF

16V

C2203

XMARK_1.8V

0

R2424

10K

R2412

0.1uF

16V

C2187

10K

R2422

0.1uF

16V

C2202

0.1uF

16V

C2217

0.1uF

16V

C2218

BLM18PG121SN1D

XMARK

L1252

0

LGDT1129

R2582

MLB-201209-0120P-N2

L1231

BLM18PG121SN1D

XMARK

L1255

0

XMARK

R2583

0.1uF

16V

C2205

1K

R2403

4 . 7 u F

16V

C2186

0.1uF

16V

C2194

0.1uF

16V

C2204

TS_2

005:AF17

0.1uF

16V

C2206

3 . 3 V _ P r o i d i o m

0

XMARK

R2588

0

XMARK

R2580

TS_6

005:AF16

0.1uF

16V

C2196

+VCCINT_1.5V

62pF

50V

50V

C2219

OPT

10K

R2409

LGDT1129

3 . 3 V _ P r o i d i o m

4 . 7 u F

XMARK

C2268

4 . 7 u F

16V

C2189

3 . 3 V _ P r o i d i o m

0

LGDT1129

R2574

GND

10K

R2408

LGDT1129

1K

R2402

0.1uF

16V

C2198

0 . 1 u F

XMARK

C2267

PM_TS_VALID

008:AP25

XMARK_1.8V

MLB-201209-0120P-N2

L1230

TS_SYNC

005:AN19

BLM18PG121SN1D

XMARK

L1254

22

R2416

0.1uF

16V

C2207

0.1uF

16V

C2210

PM_TS_CLK

008:AP25

100

R2441

0.1uF

16V

C2212

TS_1

005:AF17

PM_TS[0-7]

008:AP27

DE_H_SYSCLK

010:C16

0.1uF

16V

C2193

MSCL_3.3V

MSDA_3.3V

1K

R2404

MLB-201209-0120P-N2

L1233

100

R2444

0.1uF

16V

C2190

100

R2442

PM_TS[7]

TS_2

PM_TS[4]

TS_1

PM_TS[1]

TS_7

PM_TS[5]

TS_5

TS_6

PM_TS[0]

PM_TS[6]

PM_TS[2]

TS_3

TS_4

PM_TS[3]

TS_0

RESET

FPGA POWER

I2C

27MHz

12

37LD320H

P r o i d i o m

2 0 1 0 . 1 2 . 2 2

XMARK_1.8V

Pro:Idiom (XMARK)

P L L v o l t a g e

INNER LAYER PATERN

LGDT1129 not use XMARK

XMARK LG1001(XMARK)

Power-Up Boot Fail Trouble Shooting guide

Check P401 All

Voltage Level (3.5V, 12V, 24V)

Check power connector and

RL_ON signal OK ?

Replace Power board

Y

N

Y

Check IC1602 RESET and

UPDATE pin

Check switch SW501, SW502

Y

N

Check X1600 Clock

32.768MHz

Check X1600 application circuit

or Replace X1600

Y

N

Check IC1602 IIC communication

state

Check IIC line or replace IC1602

N

Check IR input state of IC1602

57pin

Check IR board

N

Y

Re-download PTC Micom

Y

Click on the first or last page to see other 32LD333H (CHASSIS:LA06H) service manuals if exist.