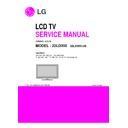

LG 22LD350 (CHASSIS:LA04A) Service Manual ▷ View online

U

S

B

D

O

W

N

S

T

R

E

A

M

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

D1452

5.6V

CDS3C05HDMI1

OPT

J

K

1

4

5

0

K

J

A

-

U

B

-

4

-

0

0

0

4

1

2

3

4

5

L1451

MLB-201209-0120P-N2

120-ohm

SIDE_USB_DP

SIDE_USB_DM

D1451

5.6V

CDS3C05HDMI1

OPT

C1451

22uF

10V

IC1450

AP2191SG-13

3

IN_2

2

IN_1

4

EN

1

GND

5

FLG

6

OUT_1

7

OUT_2

8

NC

C1452

10uF

10V

10uF

10V

+5V_USB

C1453

0.1uF

R1455

4.7K

OPT

4.7K

OPT

+3.3V_Normal

R1456

0

USB_CTL

R1454

10K

10K

R1451

47

USB_OCD

USB_DIODES

$0.077

09.09.03

LD350

14

USB

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

DDR

SDDR_A[4]

BDDR2_D[15]

TDDR_D[4]

SDDR_A[0]

TDDR_A[8]

SDDR_D[8]

TDDR_D[12]

ADDR2_D[0]

TDDR_D[9]

ADDR2_DQM1_P

SDDR_DQS0_P

BDDR2_D[3]

ADDR2_D[0-15]

TDDR_D[8]

BDDR2_A[0]

ADDR2_A[2]

SDDR_A[2]

BDDR2_A[10]

TDDR_D[11]

BDDR2_BA[1]

SDDR_CK

TDDR_A[10]

ADDR2_D[13]

ADDR2_D[13]

TDDR_D[10]

SDDR_D[3]

ADDR2_D[9]

ADDR2_A[0]

TDDR_D[7]

ADDR2_DQS0_N

ADDR2_A[8]

ADDR2_D[0]

/BDDR2_MCLK

SDDR_D[8]

ADDR2_A[10]

TDDR_BA[0]

TDDR_A[7]

BDDR2_A[3]

TDDR_A[11]

BDDR2_A[5]

SDDR_D[11]

ADDR2_A[12]

SDDR_A[4]

BDDR2_D[13]

ADDR2_A[1]

/SDDR_CK

ADDR2_DQS1_P

SDDR_D[6]

ADDR2_D[5]

TDDR_D[13]

ADDR2_A[0]

BDDR2_D[13]

ADDR2_A[5]

BDDR2_A[11]

ADDR2_D[12]

BDDR2_D[14]

BDDR2_D[11]

BDDR2_A[2]

SDDR_A[12]

TDDR_D[9]

SDDR_D[2]

ADDR2_A[5]

ADDR2_BA[1]

ADDR2_A[12]

SDDR_A[5]

BDDR2_D[1]

ADDR2_CKE

ADDR2_A[2]

BDDR2_A[7]

BDDR2_D[7]

ADDR2_A[7]

TDDR_D[14]

SDDR_A[11]

ADDR2_D[6]

TDDR_A[2]

SDDR_A[0]

SDDR_D[4]

BDDR2_D[0]

BDDR2_A[4]

BDDR2_A[12]

BDDR2_D[6]

BDDR2_D[1]

SDDR_D[5]

BDDR2_D[3]

BDDR2_DQM1_P

SDDR_D[0-15]

SDDR_D[0]

ADDR2_A[1]

BDDR2_A[5]

BDDR2_D[2]

ADDR2_DQM0_P

BDDR2_A[7]

TDDR_D[7]

BDDR2_D[10]

BDDR2_DQS0_P

ADDR2_D[2]

/TDDR_CAS

ADDR2_D[8]

ADDR2_D[10]

BDDR2_A[4]

SDDR_D[1]

SDDR_D[14]

TDDR_A[6]

TDDR_A[9]

ADDR2_A[6]

TDDR_D[1]

BDDR2_A[12]

TDDR_D[15]

BDDR2_D[5]

BDDR2_CKE

SDDR_D[13]

BDDR2_D[7]

SDDR_A[9]

SDDR_D[14]

TDDR_D[8]

ADDR2_BA[0]

BDDR2_D[4]

TDDR_D[5]

BDDR2_DQM0_P

SDDR_D[12]

SDDR_A[6]

SDDR_A[8]

TDDR_D[13]

ADDR2_ODT

SDDR_D[4]

SDDR_A[2]

SDDR_D[10]

BDDR2_D[14]

ADDR2_D[15]

TDDR_A[4]

SDDR_D[11]

/ADDR2_MCLK

BDDR2_D[12]

/SDDR_CAS

ADDR2_DQS1_N

ADDR2_D[12]

SDDR_A[10]

SDDR_A[1]

SDDR_D[1]

BDDR2_A[11]

BDDR2_DQS0_N

ADDR2_D[8]

SDDR_BA[0]

BDDR2_A[1]

ADDR2_D[15]

SDDR_A[9]

BDDR2_D[9]

TDDR_D[6]

ADDR2_D[3]

ADDR2_DQS0_P

ADDR2_D[14]

BDDR2_A[6]

/ADDR2_CAS

SDDR_A[7]

TDDR_D[12]

TDDR_A[8]

BDDR2_BA[0]

TDDR_D[11]

ADDR2_A[11]

TDDR_A[0-12]

SDDR_D[10]

BDDR2_A[0]

BDDR2_D[8]

BDDR2_DQS1_P

ADDR2_D[10]

ADDR2_A[7]

SDDR_A[6]

TDDR_D[3]

BDDR2_D[9]

TDDR_CKE

SDDR_DQS1_N

ADDR2_D[14]

ADDR2_A[11]

TDDR_A[3]

TDDR_A[7]

BDDR2_D[5]

BDDR2_A[8]

/BDDR2_WE

BDDR2_ODT

BDDR2_D[0-15]

SDDR_A[3]

TDDR_D[0]

BDDR2_D[15]

SDDR_ODT

SDDR_A[7]

TDDR_D[1]

SDDR_DQM1_P

SDDR_D[13]

ADDR2_A[4]

TDDR_D[5]

TDDR_A[0]

ADDR2_D[5]

TDDR_A[12]

SDDR_D[5]

TDDR_D[15]

ADDR2_D[7]

SDDR_A[0-12]

SDDR_BA[1]

/TDDR_MCLK

SDDR_D[0]

TDDR_D[0-15]

SDDR_D[7]

BDDR2_A[6]

ADDR2_D[6]

SDDR_A[11]

SDDR_A[8]

SDDR_A[5]

SDDR_D[6]

TDDR_MCLK

TDDR_D[2]

TDDR_A[9]

ADDR2_A[9]

SDDR_D[15]

ADDR2_D[7]

SDDR_A[3]

SDDR_DQS1_P

SDDR_A[12]

SDDR_D[15]

BDDR2_A[0-12]

TDDR_D[10]

TDDR_D[6]

BDDR2_A[9]

TDDR_DQM0_P

TDDR_A[1]

ADDR2_D[1]

BDDR2_A[10]

/ADDR2_WE

BDDR2_D[8]

/TDDR_WE

/SDDR_WE

ADDR2_A[4]

ADDR2_A[3]

ADDR2_A[10]

BDDR2_A[3]

ADDR2_MCLK

TDDR_DQS0_N

TDDR_DQS1_P

TDDR_A[3]

SDDR_D[9]

ADDR2_D[1]

BDDR2_DQS1_N

SDDR_A[1]

TDDR_DQS0_P

ADDR2_A[0-12]

BDDR2_D[4]

TDDR_A[0]

/BDDR2_CAS

TDDR_D[14]

BDDR2_D[12]

SDDR_DQM0_P

BDDR2_D[6]

BDDR2_D[0]

SDDR_D[12]

/BDDR2_RAS

BDDR2_D[10]

TDDR_A[10]

TDDR_A[4]

TDDR_D[4]

TDDR_A[2]

TDDR_D[0]

ADDR2_D[2]

SDDR_DQS0_N

/ADDR2_RAS

BDDR2_A[2]

/SDDR_RAS

TDDR_A[5]

BDDR2_A[1]

BDDR2_MCLK

SDDR_D[9]

SDDR_D[2]

BDDR2_D[2]

BDDR2_A[8]

SDDR_CKE

TDDR_A[6]

ADDR2_D[9]

BDDR2_D[11]

TDDR_D[3]

ADDR2_D[4]

ADDR2_D[11]

TDDR_BA[1]

ADDR2_D[11]

TDDR_A[5]

TDDR_D[2]

ADDR2_A[8]

TDDR_DQM1_P

ADDR2_A[9]

SDDR_D[7]

BDDR2_A[9]

/TDDR_RAS

ADDR2_A[3]

SDDR_A[10]

TDDR_DQS1_N

ADDR2_D[3]

SDDR_D[3]

TDDR_A[12]

ADDR2_D[4]

ADDR2_A[6]

TDDR_A[11]

TDDR_A[1]

ADDR2_BA[2]

BDDR2_BA[2]

TDDR_BA[2]

R40

56

C38

0.1uF

R41

56

AR5

56

AR7

56

R39

56

C25

0.1uF

C32

0.1uF

C22

0.1uF

0.1uF

AR10

56

AR3

56

C30

10uF

R21 56

R16

56

R6

56

C31

0.1uF

C18

1000pF

R34

56

R10

56

C13

10uF

C20

0.1uF

C2

1000pF

C27

0.1uF

C11

0.1uF

C24

0.1uF

C3

10uF

R24

1K

1%

C37

0.1uF

R35

56

R14

56

R17

56

+1.8V_S_DDR

AR8

56

C41

0.1uF

R19

56

R5

1K

1%

R15

56

R20

56

R23

1K

1%

C8

0.1uF

C34

0.1uF

C29

0.1uF

C14

0.1uF

+1.8V_S_DDR

AR13

56

R29

56

AR1

56

AR4

56

C10

0.1uF

R42

56

R33

56

R12

56

R38

56

C17

0.1uF

C39

0.1uF

AR12

56

AR9

56

R11

56

C5

0.1uF

R28

56

L1

BLM18PG121SN1D

R27

56

AR11

56

C35

0.1uF

C42

1000pF

1000pF

C7

0.1uF

R13

56

R30

56

+1.8V_DDR

AR2

56

R4

1K

1%

C6

0.1uF

AR14

56

C4

0.1uF

C40

0.1uF

0.1uF

R18

56

C43

0.1uF

R37

56

C15

0.1uF

C12

0.1uF

R43

56

C1

0.1uF

0.1uF

R2

150

OPT

R45

150

OPT

C33

0.1uF

R44

1K

1%

R36

56

C9

0.1uF

AR6

56

+1.8V_S_DDR

C23

10uF

+1.8V_S_DDR

C19

0.1uF

C16

0.1uF

+1.8V_S_DDR

C21

0.1uF

R7

56

C36

0.1uF

R47

1K

1%

R22

56

R8

33

R9

33

R32

33

R31

33

+1.8V_S_DDR

+1.8V_S_DDR

+1.8V_S_DDR

IC2

H5PS5162FFR-S6C

HYNIX

J2

VREF

J8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

NC4

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

IC1

H5PS5162FFR-S6C

HYNIX

J2

VREF

J8

CK

H2

VSSQ2

B7

UDQS

N8

A4

P8

A8

L1

NC4

L2

BA0

R8

NC3

K7

RAS

F8

VSSQ3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC5

L3

BA1

J7

VSSDL

L7

CAS

F2

VSSQ4

B3

UDM

M2

A10/AP

K2

CKE

R7

NC6

M7

A2

N7

A6

M8

A0

J1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC1

N2

A3

P2

A7

H8

VSSQ1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC2

E7

VSSQ5

D8

VSSQ6

D2

VSSQ7

A7

VSSQ8

B8

VSSQ9

B2

VSSQ10

P9

VSS1

N1

VSS2

J3

VSS3

E3

VSS4

A3

VSS5

G9

VDDQ1

G7

VDDQ2

G3

VDDQ3

G1

VDDQ4

E9

VDDQ5

C9

VDDQ6

C7

VDDQ7

C3

VDDQ8

C1

VDDQ9

A9

VDDQ10

R1

VDD1

M9

VDD2

J9

VDD3

E1

VDD4

A1

VDD5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

R50

0

OPT

R51

0

OPT

R49

0

OPT

R48

0

OPT

IC100

MSD3159GV

B_DDR2_A0

T26

B_DDR2_A1

AF26

B_DDR2_A2

T25

B_DDR2_A3

AF23

B_DDR2_A4

T24

B_DDR2_A5

AE23

B_DDR2_A6

R26

B_DDR2_A7

AD22

B_DDR2_A8

R25

B_DDR2_A9

AC22

B_DDR2_A10

AD23

B_DDR2_A11

R24

B_DDR2_A12

AE22

B_DDR2_BA0

AC23

B_DDR2_BA1

AC24

B_DDR2_BA2

AB22

B_DDR2_MCLK

V25

/B_DDR2_MCLK

V24

B_DDR2_CKE

AB23

B_DDR2_ODT

U26

/B_DDR2_RAS

U25

/B_DDR2_CAS

U24

/B_DDR2_WE

AB24

B_DDR2_DQS0

AB26

B_DDR2_DQS1

AA26

B_DDR2_DQM0

AC25

B_DDR2_DQM1

AC26

B_DDR2_DQSB0

AB25

B_DDR2_DQSB1

AA25

B_DDR2_DQ0

W25

B_DDR2_DQ1

AE26

B_DDR2_DQ2

W24

B_DDR2_DQ3

AF24

B_DDR2_DQ4

AF25

B_DDR2_DQ5

V26

B_DDR2_DQ6

AE25

B_DDR2_DQ7

W26

B_DDR2_DQ8

Y26

B_DDR2_DQ9

AD25

B_DDR2_DQ10

Y25

B_DDR2_DQ11

AE24

B_DDR2_DQ12

AD26

B_DDR2_DQ13

Y24

B_DDR2_DQ14

AD24

B_DDR2_DQ15

AA24

A_MVREF

D15

A_DDR2_A0

C13

A_DDR2_A1

A22

A_DDR2_A2

B13

A_DDR2_A3

C22

A_DDR2_A4

A13

A_DDR2_A5

A23

A_DDR2_A6

C12

A_DDR2_A7

B23

A_DDR2_A8

B12

A_DDR2_A9

C23

A_DDR2_A10

B22

A_DDR2_A11

A12

A_DDR2_A12

A24

A_DDR2_BA0

C24

A_DDR2_BA1

B24

A_DDR2_BA2

D24

A_DDR2_MCLK

B14

/A_DDR2_MCLK

A14

A_DDR2_CKE

D23

A_DDR2_ODT

D14

/A_DDR2_RAS

D13

/A_DDR2_CAS

D12

/A_DDR2_WE

D22

A_DDR2_DQS0

B18

A_DDR2_DQS1

C17

A_DDR2_DQM0

C18

A_DDR2_DQM1

A19

A_DDR2_DQSB0

A18

A_DDR2_DQSB1

B17

A_DDR2_DQ0

B15

A_DDR2_DQ1

A21

A_DDR2_DQ2

A15

A_DDR2_DQ3

B21

A_DDR2_DQ4

C21

A_DDR2_DQ5

C14

A_DDR2_DQ6

C20

A_DDR2_DQ7

C15

A_DDR2_DQ8

C16

A_DDR2_DQ9

C19

A_DDR2_DQ10

B16

A_DDR2_DQ11

B20

A_DDR2_DQ12

A20

A_DDR2_DQ13

A16

A_DDR2_DQ14

B19

A_DDR2_DQ15

A17

IC2-*1

A3R12E4JFF-G8E

ZENTEL

J2

VREF

J8

CK

H2

VSSQ_2

B7

UDQS

N8

A4

P8

A8

L1

NC_4

L2

BA0

R8

NC_3

K7

RAS

F8

VSSQ_3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC_5

L3

BA1

J7

VSSDL

L7

CAS

F2

VSSQ_4

B3

UDM

M2

A10

K2

CKE

R7

NC_6

M7

A2

N7

A6

M8

A0

J1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC_1

N2

A3

P2

A7

H8

VSSQ_1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC_2

E7

VSSQ_5

D8

VSSQ_6

D2

VSSQ_7

A7

VSSQ_8

B8

VSSQ_9

B2

VSSQ_10

P9

VSS_1

N1

VSS_2

J3

VSS_3

E3

VSS_4

A3

VSS_5

G9

VDDQ_1

G7

VDDQ_2

G3

VDDQ_3

G1

VDDQ_4

E9

VDDQ_5

C9

VDDQ_6

C7

VDDQ_7

C3

VDDQ_8

C1

VDDQ_9

A9

VDDQ_10

R1

VDD_1

M9

VDD_2

J9

VDD_3

E1

VDD_4

A1

VDD_5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

IC1-*1

A3R12E4JFF-G8E

ZENTEL

J2

VREF

J8

CK

H2

VSSQ_2

B7

UDQS

N8

A4

P8

A8

L1

NC_4

L2

BA0

R8

NC_3

K7

RAS

F8

VSSQ_3

F3

LDM

P3

A9

M3

A1

N3

A5

K8

CK

R3

NC_5

L3

BA1

J7

VSSDL

L7

CAS

F2

VSSQ_4

B3

UDM

M2

A10

K2

CKE

R7

NC_6

M7

A2

N7

A6

M8

A0

J1

VDDL

K3

WE

E8

LDQS

P7

A11

K9

ODT

A2

NC_1

N2

A3

P2

A7

H8

VSSQ_1

F7

LDQS

A8

UDQS

R2

A12

L8

CS

E2

NC_2

E7

VSSQ_5

D8

VSSQ_6

D2

VSSQ_7

A7

VSSQ_8

B8

VSSQ_9

B2

VSSQ_10

P9

VSS_1

N1

VSS_2

J3

VSS_3

E3

VSS_4

A3

VSS_5

G9

VDDQ_1

G7

VDDQ_2

G3

VDDQ_3

G1

VDDQ_4

E9

VDDQ_5

C9

VDDQ_6

C7

VDDQ_7

C3

VDDQ_8

C1

VDDQ_9

A9

VDDQ_10

R1

VDD_1

M9

VDD_2

J9

VDD_3

E1

VDD_4

A1

VDD_5

B9

DQ15

B1

DQ14

D9

DQ13

D1

DQ12

D3

DQ11

D7

DQ10

C2

DQ9

C8

DQ8

F9

DQ7

F1

DQ6

H9

DQ5

H1

DQ4

H3

DQ3

H7

DQ2

G2

DQ1

G8

DQ0

DDR2

DDR2 1.8V By CAP - Place these Caps near Memory

HONG YEON HYUK

LD350

09.09.03

21

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SERIAL FLASH

R104

33

+3.3V_Normal

+3.3V_Normal

Flash_WP_1

001:AR30

R102

0

OPT

SPI_CS

001:AR36

+3.3V_Normal

C126

0.1uF

0.1uF

R103

10K

SPI_DI

001:AR36

SPI_CK

001:AR35

R101

0

SPI_DO

001:AR36

R105

4.7K

L110

Q100

KRC103S

E

B

C

IC101

MX25L3205DM2I-12G

3

WP#

2

SO

4

GND

1

CS#

5

SI

6

SCLK

7

HOLD#

8

VCC

SERIAL FLASH

Serial FLASH MEMORY

for BOOT

for BOOT

LD350

09.09.03

21

THE SYMBOL MARK OF THIS SCHEMETIC DIAGRAM INCORPORATES

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

SPECIAL FEATURES IMPORTANT FOR PROTECTION FROM X-RADIATION.

FILRE AND ELECTRICAL SHOCK HAZARDS, WHEN SERVICING IF IS

ESSENTIAL THAT ONLY MANUFATURES SPECFIED PARTS BE USED FOR

THE CRITICAL COMPONENTS IN THE SYMBOL MARK OF THE SCHEMETIC.

+5V_TU

TUNER_RESET

IF_AGC

C5006

100pF

50V

100pF

50V

FE_VMAIN

R5009

100

100

+3.3V_TU

R5001

0

OPT

C5003

0.1uF

16V

16V

L5003

BLM18PG121SN1D

+3.3V_Normal

+3.3V_TU

C5024

0.1uF

16V

C5018

22uF

16V

OPT

22uF

16V

OPT

+1.26V

+5V_TU

IF_N_MSTAR

Q5005

ISA1530AC1

TU_CVBS_BUFER

E

B

C

+3.3V_TU

+3.3V_TU

C5010

0.1uF

16V

C5007

0.1uF

16V

16V

FE_TUNER_SDA

R5027

1K

OPT

R5015

100

L5002

BLM18PG121SN1D

5V_TU_Normal

R5003

0

R5018

3.3K

3.3K

C5021

0.1uF

16V

16V

R5025

4.7K

4.7K

R5026

1K

OPT

R5011

100K

C5022

0.1uF

16V

16V

C5025

100pF

50V

R5002

0

OPT

C5001

100pF

50V

100pF

50V

+3.3V_TU

R5022

1K

1K

C5016

0.1uF

16V

0.1uF

16V

C5023

0.1uF

16V

0.1uF

16V

R5032

82

82

+5V_TU

C5017

22uF

16V

OPT

22uF

16V

OPT

FE_SIF

Q5004

ISA1530AC1

E

B

C

C5020

22uF

16V

22uF

16V

R5016

100

C5019

22uF

16V

22uF

16V

IF_P_MSTAR

R5023

0

FE_TUNER_SCL

+5V_TU

+5V_Normal

R5020

3.3K

3.3K

+1.26V

R5033

1

C5028

0.1uF

16V

0.1uF

16V

C5029

10uF

10V

10uF

10V

R5034

0

R5035

0

C5004

82pF

50V

INNOTEK

L5000

INNOTEK

VCOMO

C5000

0.047uF

50V

R5000

10K

OPT

OPT

R5004

0

1/16W

5%

TU_CVBS_BUFER

R5005

2.2K

2.2K

OPT

C5005

0.1uF

OPT

R5006

47

OPT

SIFMO

R5007

5.6K

1/16W

5%

OPT

VSB_RESET

R9823

0

0

R9824

0

0

OPT

R5029

470

1608

TU5001

TDVJ-H001F

14

3.3V

13

1.2V

5

AS

12

GND

11

VIDEO

2

BST_CNTL

10

NC

4

NC[RF_AGC]

1

ANT_PWR[OPT]

17

DIF_1

9

SIF

8

NC(IF_TP)

3

+B

16

IF_AGC_CNTL

7

SDA

6

SCL

15

RESET

18

DIF_2

19

SHIELD

+5V_USB

L5004

BLM18PG121SN1D

5V_TU_USB

IC5001

AP1117EG-13

ADJ/GND

OUT

IN

R5008

120

C5002

22uF

10V

22uF

10V

R5030

220

2012

TU_CVBS_BUFER

R5031

220

2012

TU_CVBS_BUFER

R5010

100K

OPT

C5012

47pF

50V

47pF

50V

C5013

47pF

50V

47pF

50V

R5024

0

TU_CVBS_BUFER

R5012

0

0

TU_CVBS_BYPASS

ATSC_CAN TUNER

Close to the tuner

200mA

should be guarded by ground

LGIT CAN H/N TUNER for US

60mA

26

LD350

09.09.03

MStar Option

Click on the first or last page to see other 22LD350 (CHASSIS:LA04A) service manuals if exist.